I recently led a migration where a decade‑old motion control board — custom FPGA + DSP design — had to be replaced with a commercial motherboard-based solution. The business driver was clear: spare parts were unavailable, the old vendor was out of support, and we needed to preserve takt time on a high-throughput line. If you’re facing the same challenge, this playbook captures the practical, step‑by‑step approach I used to de-risk the swap while keeping production rates steady.

Why this is harder than it looks

At first glance, swapping a proprietary motion board for a commercial motherboard feels like a commodity refresh: plug in modern hardware, run drivers, job done. In practice the constraints that matter — deterministic timing, I/O latency, synchronization across axes, safety interlocks, and closed‑loop tuning — are baked into the old board’s behavior. Takt time is not just a throughput number: it’s the sum of precise timing windows across motion, vision, gating, and downstream processes. Miss one microsecond, and you can add milliseconds of jitter that cascade into missed cycles.

Principles that guided the migration

- Start with behavior, not hardware — map what the legacy board actually does: interrupts, priorities, command scheduling, and all timing envelopes.

- Preserve determinism — a commercial motherboard must be made deterministic through RTOS, hardware offload (FPGA), or real‑time networks.

- Iterate with pilots — don’t cutover whole line at once. Stage a pilot cell and validate takt under load.

- Measure early and often — instrument both the legacy and new path to compare real performance metrics.

- Keep a fast rollback plan — ensure you can revert to the legacy board quickly if timing degrades.

Migration playbook — step by step

Below is the sequence I followed. Think of it as a checklist you can adapt to your environment.

- Discovery and timing characterization

Spend time capturing the legacy board’s timing under representative load. Use logic analyzers, trace feeders, and timestamps from your PLC/SCADA. Key metrics: interrupt latency, servo loop period, jitter distribution, command-to-actuation latency, and end‑to‑end cycle time (from pick command to pick completion).

- Define acceptance criteria

Formalize what “keeping takt time” means: maximum allowed jitter, worst-case latency, and throughput with 95th/99th percentile bounds. Convert these into testable KPIs — cycle time, missed cycles per hour, and position overshoot margins.

- Hardware selection

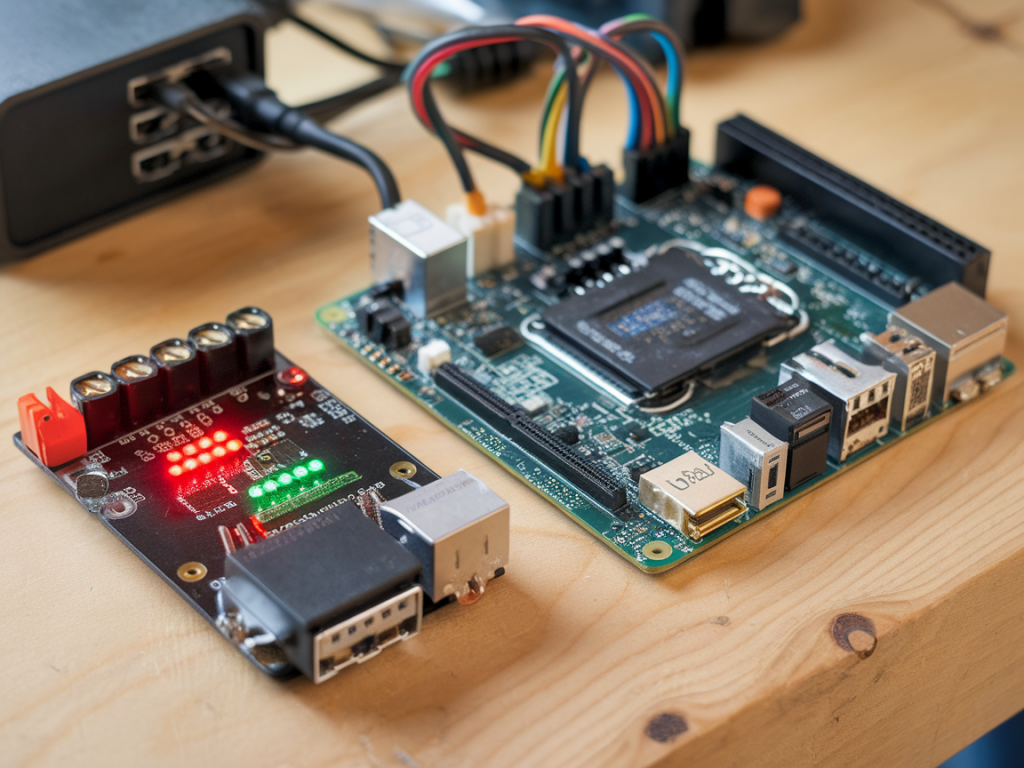

Choose a motherboard and complementary components that match the deterministic needs. Options I considered:

- Commercial industrial motherboards (e.g., Advantech, AAEON) with COM Express or ATX form factors.

- Add‑on RT cores: x86 CPU + real‑time co‑processor (Intel Atom with Atom E series + FPGA/SoC), or Intel Real-Time Extensions / real-time Linux kernels.

- Offload cards: PCIe motion controller cards (Beckhoff EtherCAT cards, Galil, Delta Tau Turbo PMAC) or small FPGAs for servo loops.

My rule: prefer a hybrid approach — a commercial motherboard for apps + a dedicated motion card/FPGA to keep tight servo loops.

- Software stack and real‑time strategy

Don’t rely on vanilla Windows or stock Linux. Choose one of:

- Real‑time Linux (PREEMPT_RT) for low-latency, hard soft‑real-time tasks.

- A real‑time hypervisor with a dedicated guest for motion control.

- Windows with an RT extension only if validated against your latency targets.

Where feasible, push the critical servo loop into hardware/firmware (FPGA or motion card). Use the motherboard host for orchestration, HMI, data logging, and non‑hard real‑time functionality.

- I/O and synchronization

Legacy boards often had tightly integrated I/O and triggered interrupts deterministically. When moving to a commercial platform:

- Use deterministic fieldbus (EtherCAT, Sercos, ProfiNet RT) or direct PCIe I/O for low latency.

- Maintain hardware triggers where timing matters; don’t try to emulate them in software only.

- Verify timestamping accuracy for sensors and vision systems; synchronization (PTP / IEEE 1588) is often necessary.

- Control algorithm porting and tuning

Port control code carefully. If your legacy board hosted PID/trajectory generation on DSP/FPGA, decide whether to:

- Reimplement on FPGA/motion card (recommended when loop frequency > 1 kHz), or

- Run on RT‑Linux with CPU affinity and highest priority, plus careful interrupt handling (for slower loops).

Expect retuning. Use automated identification routines where possible, and run step responses and disturbance injections to compare behavior to the legacy system.

- Pilot integration and shadow mode

Before cutover, run the new system in shadow mode parallel to the legacy board. Feed the same inputs and compare outputs without actuating the machine. This gives you a deterministic side‑by‑side baseline for position trajectories, timing, and edge cases.

- Stress testing and worst‑case validation

Run tests under worst-case conditions: network congestion, CPU load, sensor noise, and power variations. Measure the percent of cycles that meet the acceptance criteria. I run 48–72 hour soak tests at 1.5× nominal load to surface intermittent issues.

- Controlled cutover and rollback

Cutover by swapping one cell during a quiet production window. Keep the legacy board hot‑swapable and prepare a rollback procedure that takes less time than your maximum permissible downtime. Monitor KPIs tightly for the first 8–12 hours and be ready to pull the new system if anomalies exceed thresholds.

Common pitfalls and how I avoided them

- Underestimating interrupt jitter — I pinned critical tasks to dedicated cores and used IRQ affinity to reduce OS-induced jitter.

- Trusting default drivers — I replaced generic drivers with vendor‑optimized RT drivers for PCIe motion cards and validated DMA timings.

- Neglecting safety timing — Safety controllers must remain independent. I retained hardwired safety relays and a certified safety PLC until the new solution completed SIL validation.

- Skipping regression tests — I built automated validation scripts that replayed historical operation traces to detect behavioral drift.

Quick comparison table: legacy board vs motherboard + motion card

| Characteristic | Legacy motion board | Commercial motherboard + motion card |

|---|---|---|

| Determinism | High (hardware optimized) | High if motion card/FPGA used; otherwise variable |

| Maintainability | Low (vendor locked) | High (standard components, easier sourcing) |

| Flexibility | Limited | High (software stack, expandability) |

| Time to validate | Short (already known) | Longer (porting + testing required) |

Replacing a legacy motion control board with a commercial motherboard is feasible — and often the right business choice — but only if you treat timing and determinism as first‑class citizens. My approach is pragmatic: keep the tightest control loops in hardware or dedicated motion cards, use the motherboard for orchestration, validate with rigorous shadow testing, and always have a rollback plan. If you want, I can share a checklist template and the test scripts we used to quantify jitter and cycle compliance.